🤔 핵심정리

공부를 하며 핵심이라고 생각되는 부분을 뽑아서 정리하겠습니다.

6단원까지의 핵심정리이며 다음 단원의 핵심정리는 다음 기회에 진행하겠습니다.

컴퓨터 구조를 공부하며 포스팅을 하지 않아 이해가 덜 되었기에 틀린 부분이 있다면 지적해주세요!

🔎 2's complement code

🧐 2's complement code를 사용하는 이유는?

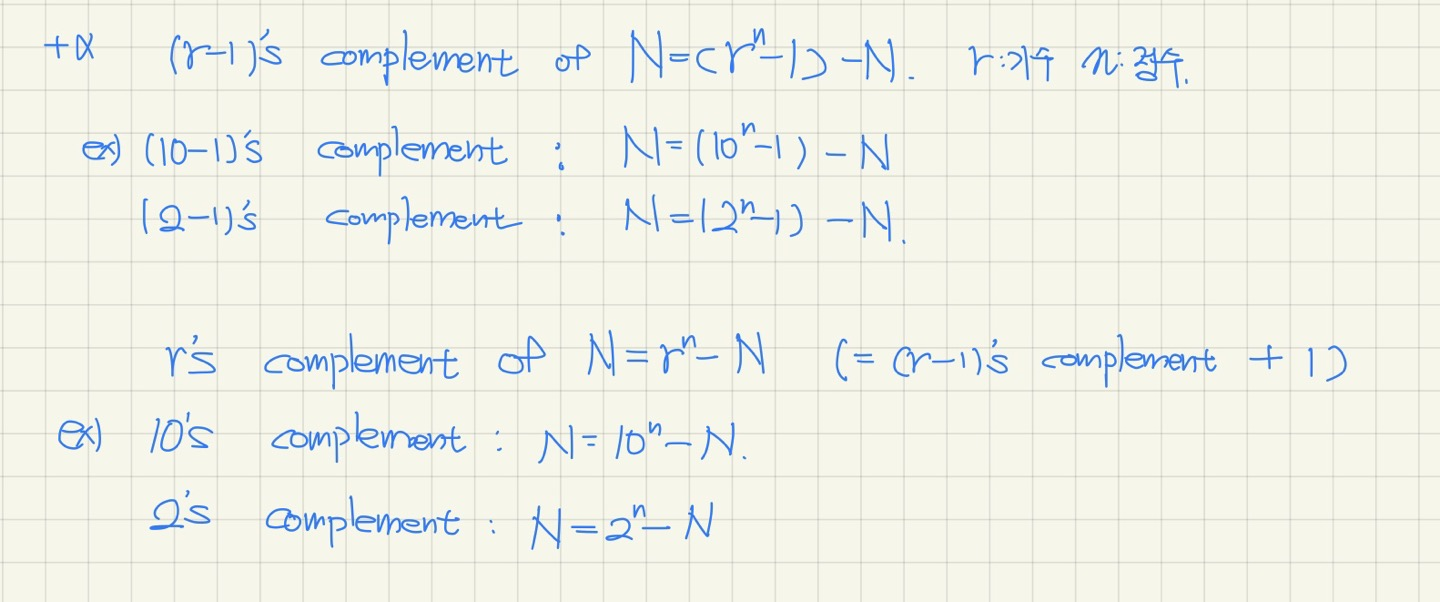

Subtraction과 logic operation을 쉽게 하기 위해서 complement를 사용하는데 컴퓨터는 이진수를 사용하므로 컴퓨터에서 해당 기능을 쉽게 하기 위해 2's complement code를 사용합니다.

+ɑ

🔎 $n$bit number addition's overflow condition

🧐 $n$bit number addition's overflow 가 발생할 필요충분 조건을 설명하시오.

$n$bit의 수 a와 b를 더한다고 했을 때 가장 왼쪽 carry를 $C_{n+1}$ 다음 carry를 $C_n$이라고 하자.

이때 $C_{n+1}$과 $C_n$의 값이 다를 때, 즉 $C_{n+1}⊕C_n = 1$ 일 떄 overflow가 발생한다.

🔎 Error Detection Codes

🧐$3$bit information을 전송함에 있어 error 검출을 위하여 odd pariti bit를 사용하려고 할 때, parity generator 및 parity checker 회로를 설계하시오

🔎 $n$ bit bus

🧐 $n$ bit bus를 mux와 three-state buffer로 구현하시오.

🔎 전가산기

🧐 Full adder를 사용하여 $4$bit adder - subtracter을 설계하시오

뺄셈 연산을 진행하기 위해서 이진수에서는 2의 보수연산을 진행합니다.

즉, $A - B = A + (~B + 1)$ 연산을 진행할 수 있는 회로를 구성해야합니다.

control signal이 1이면 $B_0 ~ B_3$의 값이 반대로 입력됩니다.

이때 $C_0 = 1$로 설정하면 $A - B = A + (~B + 1)$과 같습니다.

🔎 반가산기

🧐$4$bit binary incrementer을 설계하고 동작원리를 설명하시오

$A_3 ~ A_0$으로 이뤄진 $4$bit 수에 +1을 진행하는 회로입니다.

최하위 비트인 $A_0$를 $x$값으로 입력하고 $1$을 $y$에 입력합니다.

이때 carry는 1 또는 0인데 이를 다음 레지스터에 연쇄적으로 반영합니다.

🔎 Reference

'Computer Science > Computer Architecture' 카테고리의 다른 글

| [컴퓨터구조] 2-pass assembler (0) | 2022.10.11 |

|---|---|

| [컴퓨터구조] Interrupt Cycle (0) | 2022.10.11 |

| [컴퓨터구조] Instruction Cycle (0) | 2022.10.09 |

| [컴퓨터구조] Data Representation (0) | 2022.09.07 |

![[컴퓨터구조] 2의 보수, 오버플로우, Error Detection, n-bit bus, 전가산기, 반가산기](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FcgXFlZ%2FbtrN3UZVjzL%2F2skafvgE2X3KhwG8WwIy50%2Fimg.png)