[컴퓨터구조] Instruction Cycle

🤔 핵심정리

공부를 하며 핵심이라고 생각되는 부분을 뽑아서 정리하겠습니다.

6단원까지의 핵심정리이며 다음 단원의 핵심정리는 다음 기회에 진행하겠습니다.

컴퓨터 구조를 공부하며 포스팅을 하지 않아 이해가 덜 되었기에 틀린 부분이 있다면 지적해주세요!

🔎 Instruction Cycle

CPU가 memory로부터 프로그램된 한 개의 기계어 명령을 가져와 어떠한 동작을 요구하는 지 결정하고 명령어가 요구하는 동작들을 수행하는 과정을 Instruction Cycle이라고 합니다.

Instruction Cycle을 설명하기 전 컨트롤러의 레지스터를 살펴보겠습니다.

총 8가지의 레지스터로 명령어가 이 레지스터를 통해서 CPU내에서 어떻게 실행되는지 볼 수있습니다.

Registers

PC(Program Counter) : 프로그램 시작 시 시작의 주소를 가지고, 다음 할 프로그램의 주소를 가집니다.

AR(Address Register) : PC로 부터 실행할 메모리의 주소를 넘겨 받습니다.

IR(Instruction Register) : AR이 가진 메모리 주소에 가서 그곳의 내용(명령어)를 가져옵니다.

그리고 명령어에서 operation code 부분은 ALU로, operand(주소) 부분은 다시 AR로 줍니다.

그러면 AR은 메모리의 operand로 가서 그 내용을 DR에게 줍니다.

DR(Data Register) : AR에게 받은 값을 ALU에게 줍니다.

연산시 값을 잠시 저장할 때 쓰이기도 합니다.

AC(Accumulater) : ALU연산시 쓰입니다.

TR(Temporary Register) : 연산시 값을 잠시 저장할 때 쓰이기도 합니다.

ALU는 IR에서 op code를 받아서 DR과 AC에 저장된 값으로 연산을 합니다.

즉, ALU는 IR에서 opcode를 받아서 DR과 AD에 저장된 값으로 연산을 합니다.

ALU는 Arithmetic & Logic Unit으로 수학, 논리 연산을 하는 회로입니다.

추가로 R1은 processor register 입니다.

Instruction Cycle 과정

각 instruction cycle은 다음과 같은 subcycle로 나뉘어 집니다.

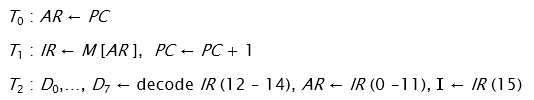

1. fetch and instruction from memory (T1)

fetch는 가져온다는 뜻으로 메모리에서 다음에 실행할 명령어를 가져온다고 보면 됩니다.

2. decode the instruction (T2)

다음은 decoding 과정으로 IR은 AR에게 받은 메모리의 주소로 가서 그곳의 명령어를 가져옵니다.

해당 명령어는 세 부분으로 나눌 수 있는데 mode bit / operation code / operand로 나눌 수 있습니다.

이 과정을 디코딩 과정이라고 합니다.

이때 $D_0 ~ D_7$은 명령에 대한 정보로 Control unit의 동작 구조를 이해해야 합니다.

Control unit

control unit은 컴퓨터 구조를 정의하는 세가지 중 하나입니다.

컴퓨터는 control signal(instruction의 선택)이 발생되는 것이 중요합니다.

레지스터는 control signal이 활성화되어 있을 때 clock이 켜지면 바뀌는데, 클럭은 아주 빠르게 켜졌다 꺼졌다 하므로 control signal이 타이밍에 맞게 활성화 되는 것이 중요합니다.

이때 control signal이 control unit에 의해 발생됩니다.

Instruction register의 명령어가 해독되어 Control Logic gates로 들어가고 Sequence Counter가 일으키는 다임값이 Control Logic gates로 들어가서 결과적으로 control signal이 도출됩니다.

3. read the effective address from memory in indirect addressing mode (T3)

memory reference 명령어는 피연사자가 존재하여 피연산자의 주소정보가 필요하기 때문에 메모리로부터 effective address를 읽기 단계를 밟아야 합니다.

하지만 register reference 명령어 또는 I/O 명령어는 피연사자가 애초에 필용ㅄ기 때문에 주소 자체가 필요없기 때문에 effective address 읽기 단계를 밟을 필요가 없습니다.

이 경우에 T3에서 instruction을 실행합니다.

IR에 fetch된 명령어가 T2에서 decode 되고나서 $D_0 ~ D_7$이 생성됩니다.($D_0 ~ D_7$은 명령어에 대한 정보입니다.)

이때 위 8가지의 신호는 명령어 코드의 15 ~ 0 비트 중에서 14, 13, 12번째 자리에 있던 비트가 만들어내는 값이었습니다.

이 값으로 명령어의 타입을 알아낼 수 있다는 뜻입니다.

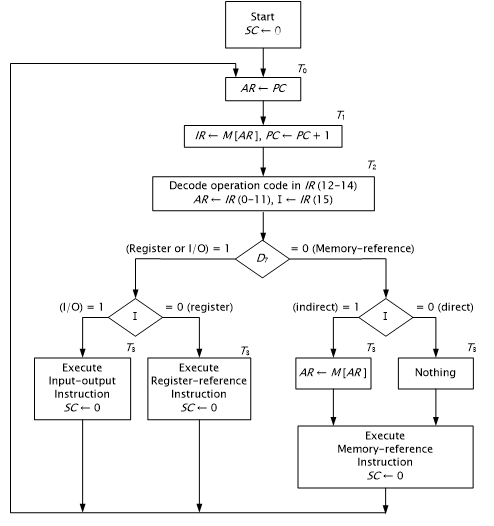

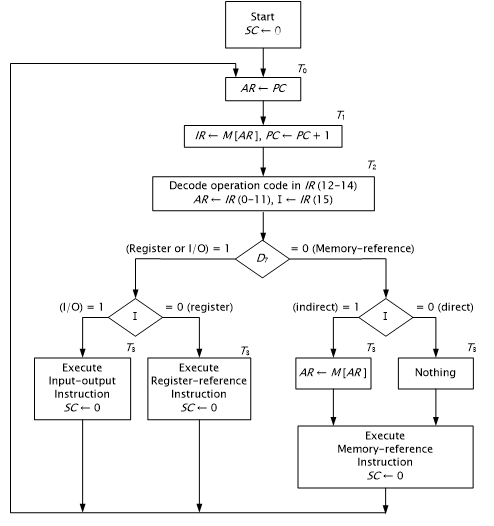

그것을 판단하는 과정은 아래의 flow chart를 통해 확인할 수 있습니다.

회로를 설명하는 과정은 중요하므로 아래에 따로 설명하도록 하겠습니다.

4. execute the instruction (T4)

다음은 실행 과정으로 어떤 명령이냐에 따라 다릅니다.

하지만 기본적으로는 우선 mode bit를 판단합니다.

mode bit는 Direct모드인지 Indirect 모드인지 판단하는데, Direct 모드인 경우 메모리의 주소값인 oprand값을 따라가서 그곳에 저장된 값을 DR에 줍니다.

반대로 Indirect모드라면 바로 메모리의 주소를 따라가서 그곳의 값을 사용하는 것이 아니라 한번 더 그 값의 주소로 가지는 메모리의 부분으로 갑니다.

즉 Direct모드에서 DR에게 준 값을 다시 한 번 AR에게 보냅니다.

그리고 그 값을 주소로 다시 메모리로 가서 찾은 값을 DR에게 넘겨줍니다.

이후의 과정은 동일힙니다.

IR에서 디코딩 과정을 통해 얻은 operation code는 ALU로 넘겨집니다.

어떤 연산인지는 opeartion code에 따라 결정되고 그 연산에 따라 DR의 값, AC에 있는 값을 통해 연산을 하고 그 결과를 AC에 저장합니다.

필요한 명령어들을 모아놓은 것을 instruction set이라고 하고 이 instruction set으로 모든 연산을 할 수 있으면 Complete instruction set이라고 합니다.

명령어는 크게 MRI / RRI / I/O instruction으로 나눌 수 있습니다.

명령어의 종류는 아래의 그림과 같습니다.

명령어에 대한 설명은 아래 Reference의 참고 블로그를 확인해주시면 감사하겠습니다.

Instruction Cycle을 flow chart를 이용하여 설명(위의 3을 자세하게 설명)

위에서 말했든 Instruction Cycle은 아래 네 개의 subcycle로 이루어집니다.

1. 메모리에서 명령어 가져오기

2. 명령어를 디코딩하기

3. Indirect addressing mode에서 메모리의 유효 주소 읽기

4. 명령 실행하기

위의 회로에서 보여주는 것은 fetch, decode후에 effective address를 읽거나 읽지 않고 최종적으로 execute 하는 과정입니다.

회로에서는 fetch, decode가 수행된 뒤를 보면 $D_7$이 0인지 1인지를 판단하고 있습니다.

두 가지 경우를 나누어 설명하겠습니다.

1) $D_7$이 1인 경우

세 비트(14, 13, 12)가 '1 1 1'이라는 뜻이며 피연산자의 주소를 다룰 필요가 없는 명령어기 때문에 AR ← M[AR] 과정은 스킵합니다.

따라서 $T_3$에 execute합니다.

2) $D_7$이 0인 경우

세 비트(14, 13, 12)가 '1 1 1'이 아닌 '0 0 0' ~ '0 1 1'의 값 중 하나라는 뜻이며, memory-reference instruction이라서 만약 indirect모드일 경우 AR ←M[AR] 과정을 거쳐야 합니다.

direct모드라면 아무 micro 연산이 일어나지 않기 때문에 $T_3$은 쉬어가는 클락이 됩니다.

즉, indirect모드라면 $T_3$에 AR에 최종적으로 값이 담기고, direct 모드라면 $T_2$에 decoding을 하는 과정에서 AR에 최종적으로 값이 저장됩니다.

$T_3$에 AR←M[AR]을 진행한 뒤 $T_4$에 execute합니다.

다음 포스팅에서는 Interrupt Cycle에 대해 알아보겠습니다.

🔎 Reference

https://m.blog.naver.com/PostView.naver?isHttpsRedirect=true&blogId=sanghun0318&logNo=220071961671

-명령어의 수행 과정

간단한 마누 컴퓨터의 CPU 내부 입니다. 사실 저번 글의 그림과 같은데 좀 세부화 시켰습니다. 메모리와...

blog.naver.com

https://splendidlolli.tistory.com/391

[컴퓨터구조] 16비트 컴퓨터 설계하기 - Instruction Cycles

우리는 16비트 컴퓨터를 설계하고 있다. 이전 포스팅([컴퓨터구조] 16비트 컴퓨터 설계하기 - Control unit 설계)에서는 Control unit을 공부했는데 여기서 timeT0, T1, ...의 발생을 보았고, 특히 fetch와 decode

splendidlolli.tistory.com

https://splendidlolli.tistory.com/392

[컴퓨터구조] 16비트 컴퓨터 설계하기 - 명령어의 실행단계에서 벌어지는 일들

배경지식 [컴퓨터구조] 16비트 컴퓨터 설계하기 - Instruction Cycles 위 글에서 명령어가 수행되는 사이클을 공부했다. ■ 타이밍 T0, T1에서 일어나는 fetch과정, ■ 타이밍 T2에서 일어나는 decode과정,

splendidlolli.tistory.com